## **AK7712A-VT**

Built-in 20-bit ADC/DAC Sophisticated Audio DSP

#### **General Description**

The AK7712A is a DSP(Digital Signal Processor) with built-in high performance 20bit 2ch ADC and 4ch DAC, on purposeto control the sound field. It is possible to calculate 383 steps on 44.1kHz and 48kHz sampling respectively. In case of 32kHz sampling, it can caluculate up to 511 steps. With a combination of this LSI and external memory for delay data, it can be easily to control the sound field such as Echo, Surround Presence Controller, and Key-control which are needed forsomething like Karaoke. Parametric Equalizing can be done without external memory.

#### Features

## [DSP unit]

- □ Word length: 24-bit (data RAM)

- □ Instruction cycle time: 54ns(maximum speed)

- $\square \quad \text{Multiplier: } 24 \times 16 \rightarrow \text{ 40-bit}$

- $\Box$  Divider: 16 ÷ 16 → 16-bit

- □ Program RAM: 384 × 32 bit

- External memory: DRAM, Pseudo-SRAM and SRAM can be connected (only use for delay data).

- □ Sampling frequency: 32kHz~48kHz

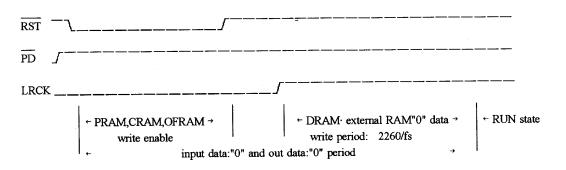

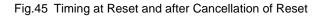

- Automatic clear function of external RAM:

47msec after bringing RST high at fs=48kHz (include internal data RAM)

- Microcomputer interface: synchronized signal type 8-bit serial input 1 channel, synchronized signal type 24-bit serial output 1 channel

- Master clock: 512(511)/384(383)/256(255)fs

The value inside () is maximum calculation steps.

512fs mode is available when 32kHz sampling is chosen.

- Conversion of master/slave mode for LRCK and BCLK:

When master mode is selected, the outputs of LRCK and BCLK depend on the set-up for input format.

- □ Serial input ports(2~4ch), and output ports(2~6ch) : 16/20/24 bit words

[ ADC unit ]

- $\square$  20-bit 64  $\times$  Oversampling  $\Delta\Sigma$  ADC: 2ch

- □ S/(N+D): 92dB

- DR, S/N: 98dB

[DAC unit]

- $\square$  20-bit 128 × Oversampling  $\Delta\Sigma$  DAC: 4ch

- □ S/(N+D): 86dB

- □ DR, S/N: 97dB

- □ Digital HPF (fc=1Hz)

```

[Total]

```

- □ Power supply: +5V

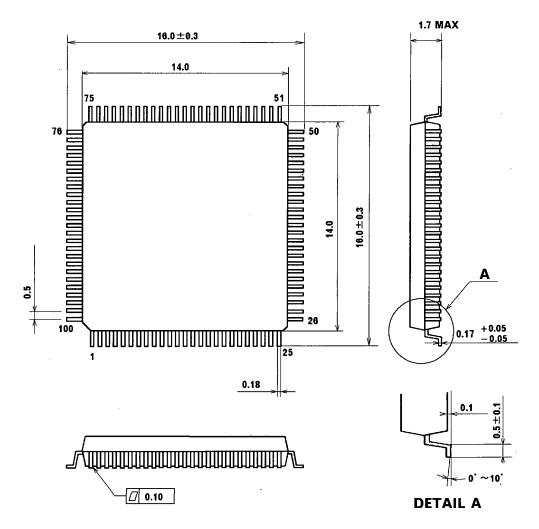

- □ Package: 100pin LQFP(0.5mm pitch)

|                                                     | Detail Features                                                                                            |                            |  |  |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|

| 1) Calculate Unit                                   |                                                                                                            |                            |  |  |  |  |

| •Multiplication:                                    | 24-bit $\times$ 16-bit $\rightarrow$ 40-bit(fixed-point, 2 instruction cycl                                | e time)                    |  |  |  |  |

| •Division:                                          | 16-bit $\div$ 16-bit(fixed-point, 17 instruction of                                                        | -                          |  |  |  |  |

| •ALU:                                               | 34-bit arithmetic operation                                                                                |                            |  |  |  |  |

| , ( <u>E</u> O.                                     | 24-bit arithmetic logic operation                                                                          |                            |  |  |  |  |

| •Shift:                                             | 1-,2-,3-,4-,6-,8-,15-bit right/left shift                                                                  |                            |  |  |  |  |

| or int.                                             | AK7712A has indirect shift function.                                                                       |                            |  |  |  |  |

|                                                     | (A shift using DBUS data can not use DBUS                                                                  |                            |  |  |  |  |

|                                                     | as multiplication input.)                                                                                  |                            |  |  |  |  |

| •Register:                                          | 34-bit × 4(ACC) [for ALU]                                                                                  |                            |  |  |  |  |

| Register.                                           | 24-bit × 8(TMP) [for DBUS connection]                                                                      |                            |  |  |  |  |

|                                                     |                                                                                                            |                            |  |  |  |  |

| <ul> <li>Double precision opera</li> </ul>          |                                                                                                            |                            |  |  |  |  |

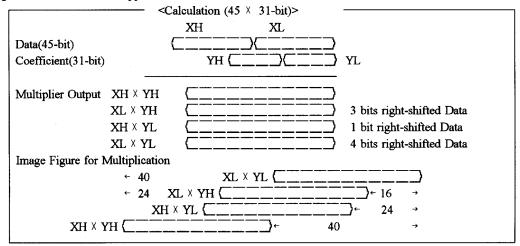

|                                                     | 24-bit(data)×31-bit(coefficient), $45 \times 31$ , $45 \times 16$                                          |                            |  |  |  |  |

| 2) Internal Memory                                  | 204 word x 22 hit                                                                                          |                            |  |  |  |  |

| Program RAM:     Date DAM                           | 384 word $\times$ 32-bit                                                                                   |                            |  |  |  |  |

| •Data RAM:                                          | 128 word $\times$ 24-bit                                                                                   |                            |  |  |  |  |

| •Coefficient RAM:                                   | 256 word × 16-bit                                                                                          |                            |  |  |  |  |

| •Offset RAM:                                        | 40 word $\times$ 16-bit (for external memory access)                                                       |                            |  |  |  |  |

| <ul> <li>Microcomputer buffer:</li> </ul>           | 16 word $\times$ 16-bit                                                                                    |                            |  |  |  |  |

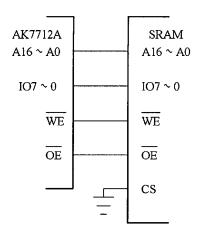

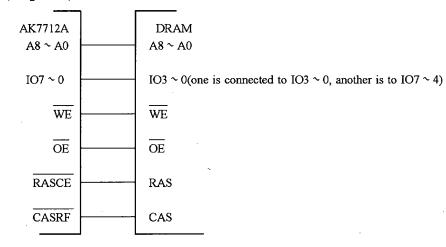

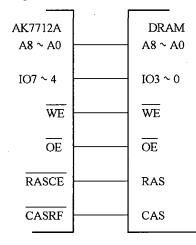

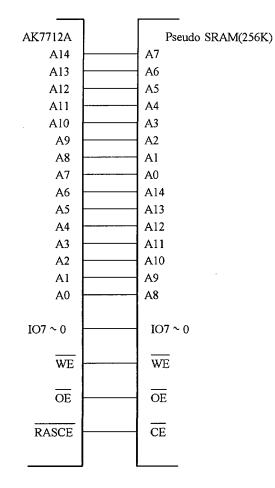

|                                                     | s (SRAM•Pseudo-SRAM•DRAM)                                                                                  |                            |  |  |  |  |

| <ul> <li>Objective memory:</li> </ul>               | 256k(32k $\times$ 8-bit),1M(128k $\times$ 8-bit) $\times$ 1 / SRAM                                         |                            |  |  |  |  |

|                                                     | $256k(32k \times 8-bit), 1M(128k \times 8-bit) \times 1 / Pseudo-SRA$                                      |                            |  |  |  |  |

|                                                     | $256k(64k \times 4\text{-bit}), 1M(256k \times 4\text{-bit}) \times 2 \text{ or } \times 1 \text{ / DRAM}$ | 1                          |  |  |  |  |

|                                                     | (Half volume of 1M DRAM is used as 512k memory                                                             | .)                         |  |  |  |  |

| <ul> <li>Treating bit length:</li> </ul>            | 16-bit (24-bit is available, but double time is needed                                                     | for access.)               |  |  |  |  |

| <ul> <li>The number of times to</li> </ul>          | access:                                                                                                    |                            |  |  |  |  |

|                                                     | SRAM, 256k Pseudo-SRAM ; 76 at 384fs                                                                       |                            |  |  |  |  |

|                                                     | : DRAM, 1M Pseudo-SRAM ; 64 at 384fs (32 at c                                                              | one DRAM)                  |  |  |  |  |

|                                                     | : SRAM, 256k Pseudo-SRAM ; 51 at 256fs                                                                     | -                          |  |  |  |  |

|                                                     | : DRAM, 1M Pseudo-SRAM ; 42 at 256fs (21 at c                                                              | one DRAM)                  |  |  |  |  |

| <ul> <li>Memory access time:</li> </ul>             |                                                                                                            |                            |  |  |  |  |

|                                                     | less than 100nsec                                                                                          |                            |  |  |  |  |

| <ul> <li>Maximum address leng</li> </ul>            | jth:                                                                                                       |                            |  |  |  |  |

|                                                     | 65535 sampling times (at 1M SRAM)                                                                          |                            |  |  |  |  |

|                                                     | 2.048sec at 32kHz, 1.486sec at 44.1kHz, 1.365sec                                                           | at 48kHz                   |  |  |  |  |

| 4) Input/Output Port                                |                                                                                                            |                            |  |  |  |  |

| •Input: 2ch analog inp                              | ut: 20-bit ADC, DR=98dB (16-bit at BCLK=32fs)                                                              |                            |  |  |  |  |

|                                                     | [when built-in ADC is connected.]                                                                          |                            |  |  |  |  |

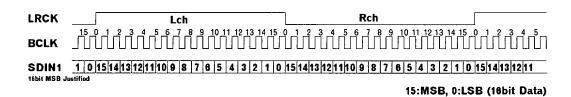

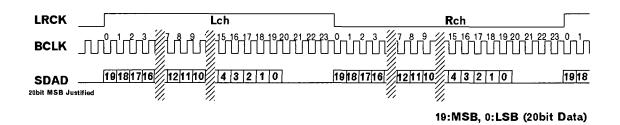

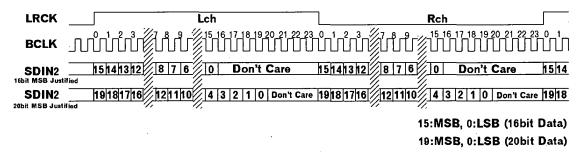

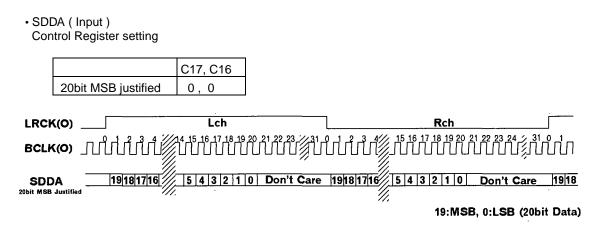

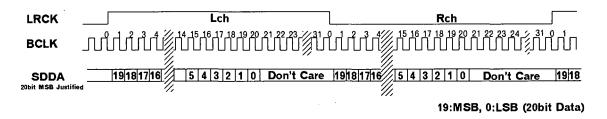

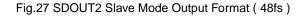

| 2ch digital inpu                                    | it: MSB justified 20-bit (16bit at BCLK=32fs)                                                              | ····MSB first serial input |  |  |  |  |

| zon digital inpu                                    | [when built-in ADC is isolated.]                                                                           |                            |  |  |  |  |

|                                                     |                                                                                                            |                            |  |  |  |  |

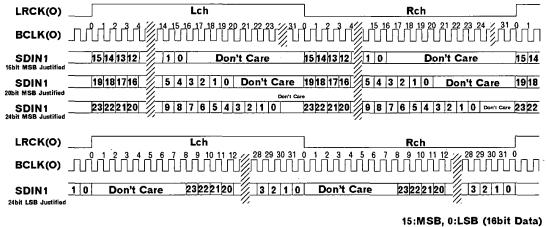

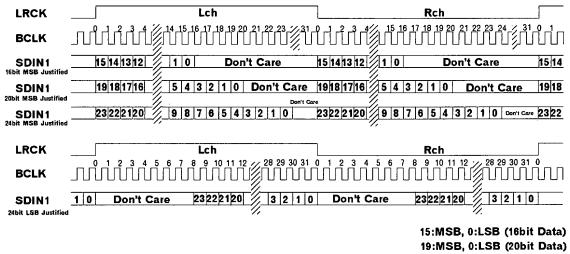

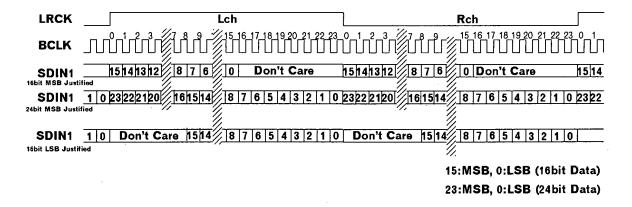

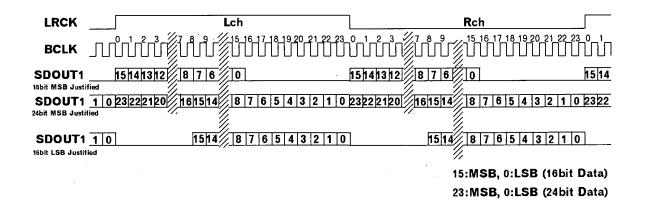

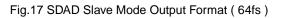

| <b>v</b> .                                          | t: MSB justified 16-•24-bit / LSB justified 16-•24-bit                                                     | ···MSB first serial input  |  |  |  |  |

| •Output: 4ch analog out                             | put: 20-bit DAC, DR=97dB(16-bit at BCLK=32fs)                                                              |                            |  |  |  |  |

|                                                     | [when built-in ADC is connected.]                                                                          |                            |  |  |  |  |

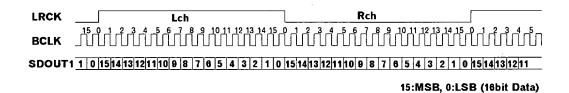

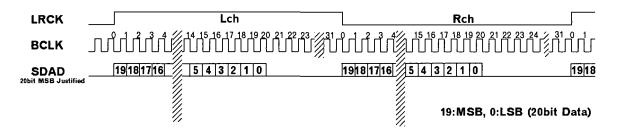

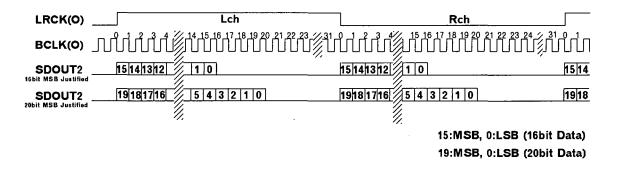

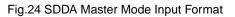

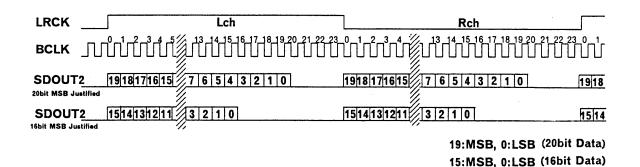

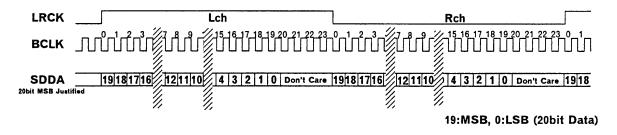

| 4ch digital outp                                    | out: MSB justified 20-bit (16bit at BCLK=32fs)                                                             | ····MSB first serial outp  |  |  |  |  |

|                                                     | [when built-in ADC is isolated.]                                                                           |                            |  |  |  |  |

| 2ch digital outr                                    | out: MSB justified 16- •24-bit/ LSB justified 16-bit                                                       | ···MSB first serial outp   |  |  |  |  |

| 5) Cascade connection with                          |                                                                                                            |                            |  |  |  |  |

| 6) Interface to Microcomput                         | •                                                                                                          |                            |  |  |  |  |

| e,enace te microcomput                              | synchronized 8-bit serial input / synchronized 24-bit                                                      | serial output              |  |  |  |  |

|                                                     | oynomized o bit send input / synomonized 24-bit                                                            | oonal output               |  |  |  |  |

| 7) Calculation Cycle:                               | max 18 432MHz(54nsec) [at 48 0kHz_384fe_5\/]                                                               |                            |  |  |  |  |

| 7) Calculation Cycle:<br>8) Master/Slave conversion | max 18.432MHz(54nsec) [at 48.0kHz, 384fs, 5V]<br>of LRCK BCLK is possible                                  |                            |  |  |  |  |

| 7) Calculation Cycle:<br>8) Master/Slave conversion |                                                                                                            |                            |  |  |  |  |

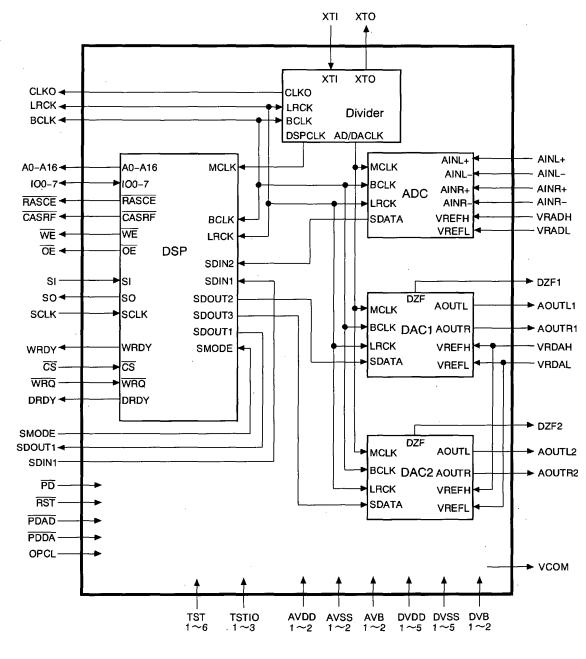

## AK7712A Block Diagram

1) ADC, DAC Inside Connection Mode (OPCL: L)

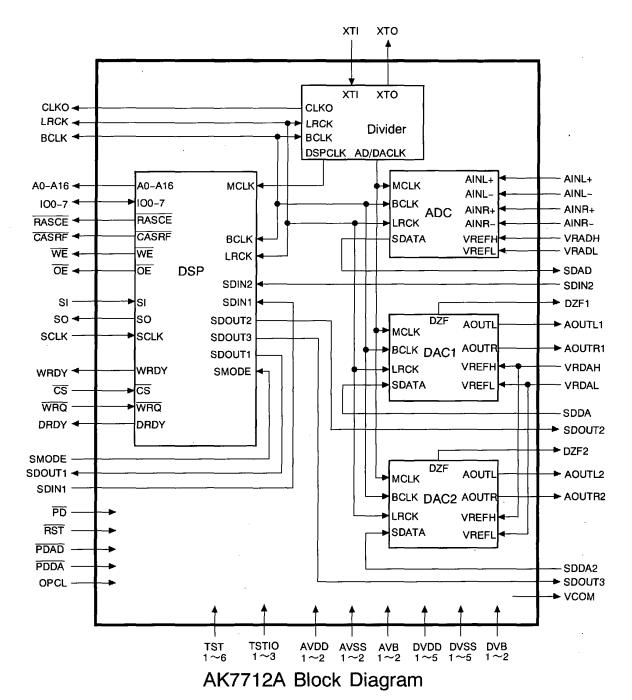

AK7712A Block Diagram

Note: Please use SDIN2,SDDA and SDDA2 with "L" or open. SDAD,SDOUT2 and SDOUT3 output "L".

2) ADC, DAC Outside Connection Mode (built-in ADC, DAC isolation mode) (OPCL:H)

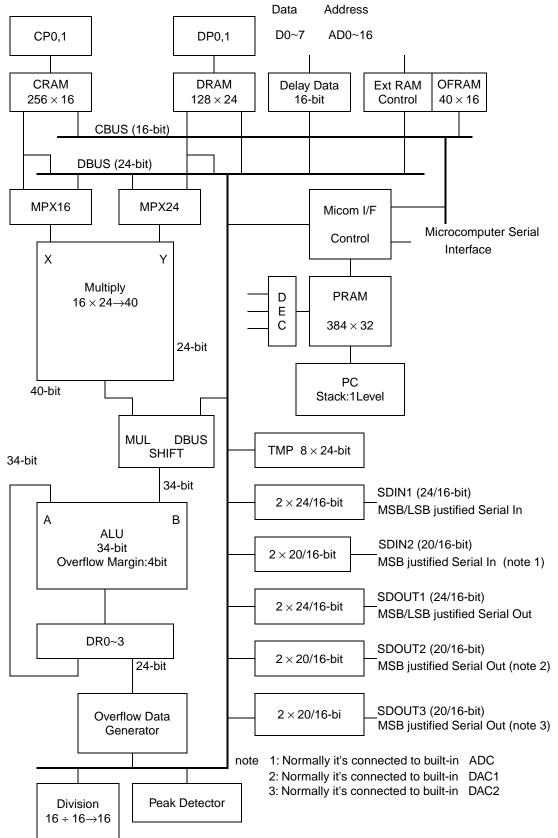

## AK7712A DSP unit Block Diagram

## Ordering Guide

```

AK7712A-VT -40~+85°C 100pin LQFP

AKD7712A Evaluation Board

```

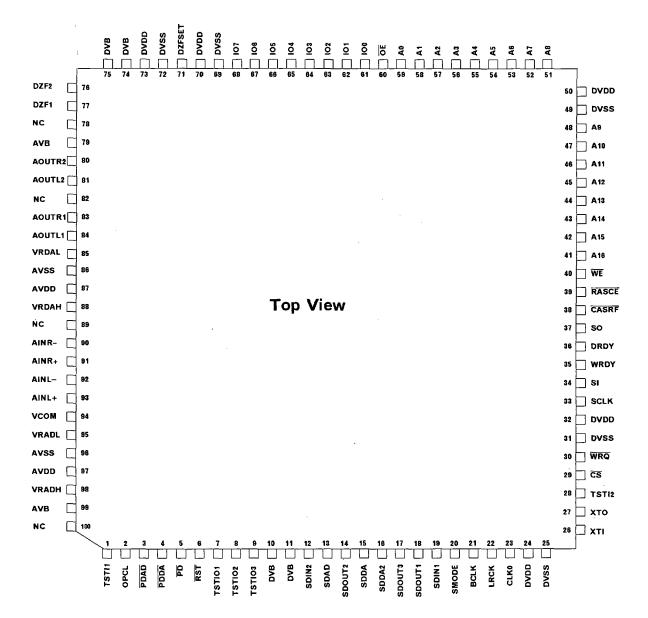

### Pin Layout

## Pin / Function

## Power Supply

| Pin No.     | Pin name | I/O | Function                       |

|-------------|----------|-----|--------------------------------|

| 24, 32, 50, | DVDD     | -   | Digital power supply           |

| 70, 73      |          |     |                                |

| 25, 31, 49, | DVSS     | -   | Digital ground                 |

| 69, 72      |          |     |                                |

| 87, 97      | AVDD     | -   | Analog power supply            |

| 86, 96      | AVSS     | -   | Analog ground                  |

| 79, 99      | AVB      | -   | Analog substrate power supply  |

| 10, 11, 74, | DVB      | -   | Digital substrate power supply |

| 75          |          |     |                                |

## External RAM Interface Signal

| Pin No. | Pin name | I/O | Function                              |

|---------|----------|-----|---------------------------------------|

| 41~48,  | A16~A0   | 0   | Address output for external RAM       |

| 51~59   |          |     | (A0:LSB justified, A16:MSB justified) |

| 40      | WE       | 0   | Write signal output                   |

|         |          |     | for external SRAM/ Pseudo-SRAM/ DRAM  |

| 39      | RESCE    | 0   | RAS for external DRAM                 |

|         |          |     | / Pseudo-SRAM-CE                      |

| 38      | CASRF    | 0   | CAS for external DRAM                 |

|         |          |     | / Pseudo-SRAM refresh                 |

| 61~68   | 100~107  | I/O | Data input/output for external RAM    |

| 60      | OE       | 0   | Output enable signal output           |

|         |          |     | for external SRAM/ Pseudo-SRAM/ DRAM  |

| Pin No. | Pin name | I/O | Function                          |

|---------|----------|-----|-----------------------------------|

| 30      | WRQ      | I   | Command register reset input      |

|         |          |     | for microcomputer interface       |

| 33      | SCLK     | Ι   | Clock input for serial data input |

|         |          |     | for microcomputer interface       |

| 36      | DRDY     | 0   | Output data ready output          |

|         |          |     | for microcomputer interface       |

| 34      | SI       | Ι   | Serial data input                 |

|         |          |     | for microcomputer interface       |

| 37      | SO       | 0   | Serial data output                |

|         |          |     | for microcomputer interface       |

|         |          |     | (Hi-Z state at CS="H")            |

| 35      | WRDY     | 0   | Data write ready output           |

|         |          |     | for microcomputer interface       |

|         |          |     | (Hi-Z state at CS="H")            |

| 29      | CS       | Ι   | Chip select input                 |

|         |          |     | for microcomputer interface       |

## ■ Microcomputer Interface Signal, Controls Signal, Input/Output Data, Reset, etc.

## ■ AK7712A Control Signal, Input/Output Data Signal, Reset, etc.

| Pin No | Pin name | I/O | Function                                                           |          |

|--------|----------|-----|--------------------------------------------------------------------|----------|

| 6      | RST      | Ι   | Reset input ("L" Reset)                                            | (note 1) |

| 5      | PD       | Ι   | Power down                                                         | (note 1) |

| 3      | PDAD     | Ι   | AD reset control                                                   | (note 1) |

| 4      | PDDA     | I   | DA reset control                                                   | (note 1) |

| 19     | SDIN1    | I   | Serial data input 1                                                |          |

|        |          |     | MSB justified 1624-bit / LSB justified 1624-bit                    |          |

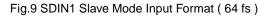

| 18     | SDOUT1   | 0   | Serial data output 1                                               |          |

|        |          |     | MSB justified 1624-bit / LSB justified 16-bit                      |          |

| 12     | SDIN2    | Ι   | Serial data input 2 (OPCL : "H" )                                  | (note 2) |

|        |          |     | MSB justified 1620-bi                                              |          |

| 13     | SDAD     | 0   | Serial data output 2 (OPCL : "H" )                                 | (note 3) |

|        |          |     | MSB justified 1620-bit, common set-up with SDIN2                   |          |

| 15     | SDDA     | I   | Serial data input 3 (OPCL : "H" )                                  | (note 2) |

|        |          |     | MSB justified 1620-bit, common set-up with SDOUT2                  |          |

| 14     | SDOUT2   | 0   | Serial data output 3 (OPCL : "H" )                                 | (note 3) |

|        |          |     | MSB justified 1620-bit                                             |          |

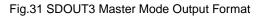

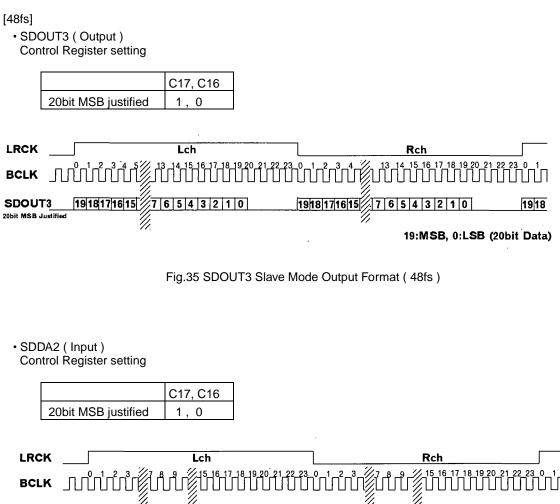

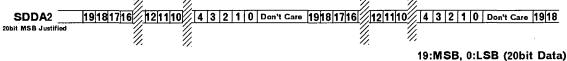

| 16     | SDDA2    | I   | Serial data input 4 (OPCL : "H")                                   | (note 2) |

|        |          |     | MSB justified 20-bit (16-bit at BCLK=32fs )                        |          |

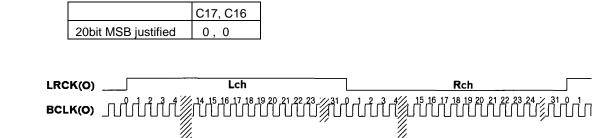

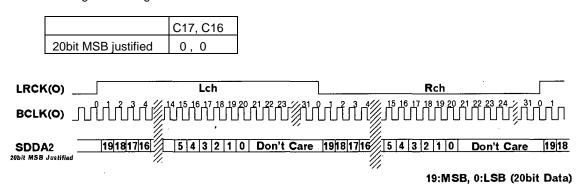

| 17     | SDOUT3   | 0   | Serial data output 4 (OPCL : "H")                                  | (note 3) |

|        |          |     | MSB justified 20-bit (16-bit at BCLK=32fs)                         |          |

| 21     | BCLK     | I/O | Clock input/output for serial data input                           |          |

| 22     | LRCK     | I/O | L/R channel identify signal input/output                           |          |

|        |          |     | Interface clock select                                             |          |

| 20     | SMODE    | I   | Input/output set-up for each clock pin of LRCK and BCLK            |          |

|        |          |     | "L":slave mode(21,22 input), "H":master mode(output)               |          |

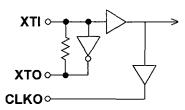

| 23     | CLKO     | 0   | Master clock output                                                | (note 4) |

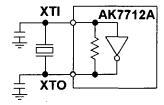

| 27     | ХТО      | 0   | Output for quartz oscillator                                       |          |

|        |          |     | When an external clock is input, this pin should be left floating. |          |

| 26     | XTI      | Ι   | Input for quartz oscillator                                        |          |

|        |          |     | A crystal can be connected between this pin and XTO, or an exter   | nal CMOS |

|        |          |     | clock can be input on this pin.                                    |          |

note:1 About the directions, please refer the paragraph of power down reset control on P.65. 2 Set to "L" or "open" when OPCL is "L".

3 The output is "L" when OPCL is "L".

4 During a timing of changing CONTROL REGISTER, CLKO is instability.

## Analog Relational Pins

| Pin No. | Pin name | I/O | Function                               |

|---------|----------|-----|----------------------------------------|

| 93      | AINL+    | Ι   | ADC Lch analog non-inverted input      |

| 92      | AINL-    | Ι   | ADC Lch analog inverted input          |

| 91      | AINR+    | I   | ADC Rch analog non-inverted input      |

| 90      | AINR-    | I   | ADC Rch analog inverted input          |

| 84      | AOUTL1   | 0   | DAC1 Lch analog output 1               |

| 83      | AOUTR1   | 0   | DAC1 Rch analog output 1               |

| 81      | AOUTL2   | 0   | DAC2 Lch analog output 2               |

| 80      | AOUTR2   | 0   | DAC2 Rch analog output 2               |

| 85      | VRDAL    | I   | Standard voltage input of DAC unit     |

|         |          |     | (normally connected to analog ground)  |

| 88      | VRDAH    | I   | Standard voltage input of DAC unit     |

|         |          |     | (normally connected to 87 pin.         |

|         |          |     | 0.1u and 10uF capacitor are connected  |

|         |          |     | between this pin and VRDAL pin.)       |

| 95      | VRADL    | I   | Standard voltage input of ADC unit     |

|         |          |     | (normally connected to analog ground)  |

| 98      | VRADH    | I   | Standard voltage input of ADC unit     |

|         |          |     | (normally connected to 97 pin.         |

|         |          |     | 0.1u and 10uF capacitor are connected  |

|         |          |     | between this pin and VRADL pin.)       |

| 94      | VCOM     | 0   | Common voltage                         |

|         |          |     | (0.1u and 10uF capacitor are connected |

|         |          |     | between this pin and analog ground.)   |

## Test Pin, etc.

| r       |          |     |                                                     |

|---------|----------|-----|-----------------------------------------------------|

| Pin No. | Pin name | I/O | Function                                            |

| 77      | DZF1     | 0   | Zero input find (for DAC1)                          |

| 76      | DZF2     | 0   | Zero input find (for DAC2)                          |

| 1       | TSTI1    | I   | Test input 1 ; use as "L" or open                   |

| 28      | TSTI2    | I   | "L": CLKO(23pin) output                             |

|         |          |     | "H": CLKO(23pin)→"L"                                |

| 7       | TSTIO1   | I/O | Test input 1 ; use as "L" or open                   |

| 8       | TSTIO2   | I/O | Test input 2 ; use as "L" or open                   |

| 9       | TSTIO3   | I/O | Test input 3 ; use as "L" or open                   |

| 2       | OPCL     | Ι   | ADC,DAC connection choice                           |

|         |          |     | "L": connect , "H": separate                        |

| 71      | DZFSET   | Ι   | Zero point find set                                 |

|         |          |     | "H": DZF output , "L": DZF output $\rightarrow$ "L" |

| 78, 82, | NC       | -   | NC pins do not be bonded inside.                    |

| 89, 100 |          |     |                                                     |

## Absolute Maximum Ratings

| Parameter                           | Symbol | min  | max      | Unit |

|-------------------------------------|--------|------|----------|------|

| DC Power supply: analog power       | VA     | -0.3 | 6.0      | V    |

| digital power(DVDD) (note 2)        | VD     | -0.3 | (VB)+0.3 | V    |

| substrate power(AVB,DVB)            | VB     | -0.3 | 6.0      | V    |

| Input current (except power supply) | IIN    | -    | ±10      | mA   |

| Analog input voltage                | VINA   |      |          |      |

| AINL+,AINL-,AINR+,AINR-,VREF        |        | -0.3 | (VA)+0.3 | V    |

| Digital input voltage (note 2)      | VIND   | -0.3 | (VB)+0.3 | V    |

| Ambient temperature                 | Та     | -40  | 85       | °C   |

| Storage temperature                 | Tstg   | -65  | 150      | °C   |

note 1: All the value mean the voltage against the ground pin.

2: Maximum absolute value must be within 6.0V, i.e. VB+0.3V  $\leq$  6.0V.

Warning: To operate beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

## **Recommended Operating Conditions**

#### (AVSS,DVSS=0V; note 1)

| Parameter                  | Symbol | min  | typ | max  | Unit |  |  |  |

|----------------------------|--------|------|-----|------|------|--|--|--|

| Power supply: analog power | VA     | 4.75 | 5.0 | 5.25 | V    |  |  |  |

| digital power (DVDD)       | VD     | 4.75 | 5.0 | VB   | V    |  |  |  |

| substrate power (AVB,DVB)  | VB     | 4.75 | 5.0 | 5.25 | V    |  |  |  |

(note 2,3,4)

note 1: All the value mean the voltage against the ground pin.

2: The VA and VB should be powered at the same time or earlier than VD.

3: The VA and VB are connected together through the chip substrate and has several ohms resistors. The VA and VB should be supplied from the same power unit.

4: Analog input/output voltages are proportional to the voltages of VRADH, VRDAH.

\* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

### Analog Characteristics

(Ta=25°C; AVDD,DVDD,AVB,DVB=5.0V; VRADH=AVDD,VRADL=AVSS,VRDAH=AVDD,VRDAL=AVSS;

measurement band width=10Hz~20kHz; DSP unit is reset; ADC differential input; unless otherwise specified.)

| Parameter                                | min  | typ  | max  | Units  |

|------------------------------------------|------|------|------|--------|

| ADC unit :                               | -    | -    | -    |        |

| Resolution                               |      |      | 20   | Bits   |

| Dynamic characteristics                  | -    | -    | -    |        |

| S/(N+D) (-0.5dB)                         | 86   | 92   |      | dB     |

| S/N (A-Weight)                           | 94   | 98   |      | dB     |

| Dynamic range (A-Weight) (note 1)        | 94   | 98   |      | dB     |

| Interchannel isolation (f=1kHz)          | 90   | 105  |      | dB     |

| DC Accuracy                              |      |      |      |        |

| Interchannel gain mismatch               |      | 0.1  | 0.3  | dB     |

| Gain drift                               | -    | 50   | -    | ppm/°C |

| Analog input                             | -    | -    | -    |        |

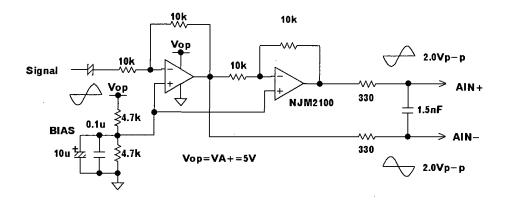

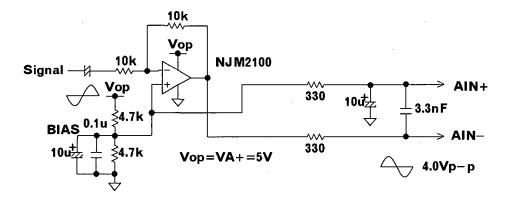

| Input voltage (note 2)                   | ±1.9 | ±2.0 | ±2.1 | Vp-р   |

| Input impedance                          |      | 220  |      | kΩ     |

| DAC unit :                               |      |      |      |        |

| Resolution                               |      |      | 20   | Bits   |

| Dynamic characteristics                  |      |      |      |        |

| S/(N+D) ( 0 dB )                         | 80   | 86   |      | dB     |

| S/N (A-Weight)                           | 93   | 97   |      | dB     |

| Dynamic range (A-Weight) (note 1)        | 93   | 97   |      | dB     |

| Interchannel isolation (f=1kHz) (note 4) | 90   | 105  |      | dB     |

| DC Accuracy                              |      |      |      |        |

| Interchannel gain mismatch (note 4)      |      | 0.2  | 0.5  | dB     |

| Gain drift                               | -    | 50   | -    | ppm/∘C |

| Analog output                            |      |      |      |        |

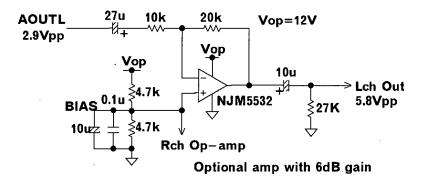

| Output voltage (note 3)                  | 2.65 | 2.90 | 3.15 | Vp-p   |

| Load resistance                          | 5    |      |      | kΩ     |

note 1: S/(N+D) with an input signal of -60dB below full-scale.

2: The full-scale of analog input voltage(AIN = (AIN+) - (AIN-) ) equals to

$\pm$ FS =  $\pm$ (VRADH - VRADL)  $\times$  0.4

3: The full-scale of output voltage(0dB) is proportional to VRDAH.

Aout(typ. @0dB) =  $2.9Vpp \times VRDAH/5$

4: Between L channel and R channel of each DAC.

fs=44.1kHz; BCLK=64fs master mode; MCLK=256fs; input signal frequency=1kHz; 20-bit;

## **Digital Filter Characteristics**

This data is not the guaranteed characteristic value but the designed value as a reference.

#### ADC unit :

(Ta=25°C; VA, VD, VB=5.0V±5%; fs=44.1kHz)

|              | Parameter  |            | Symbol | min   | typ  | max    | Units |

|--------------|------------|------------|--------|-------|------|--------|-------|

| Passband     | (±0.06dB)  |            | PB     | 0     |      | 20.00  | kHz   |

|              | ( -6.0 dB) | (note 1)   |        | 0     |      | 22.05  | kHz   |

| Stopband     |            | (note 1)   | SB     | 24.35 |      |        | kHz   |

| Passband rip | ple        | (note 2)   | PR     |       |      | ±0.005 | dB    |

| Stopband att | enuation   | (note 3,4) | SR     | 80    |      |        | dB    |

| Group delay  | distortion |            | ∆GD    |       |      | 0      | us    |

| Group delay  |            | (Ts=1/fs)  | GD     |       | 29.3 |        | Ts    |

note 1: The frequencies of passband/stopband are proportional to the sampling frequency (fs).

2: Passband is DC to 19.75kHz at fs=44.1kHz.

3: Stopband is 27.56kHz to 2.795MHz at fs=44.1kHz.

4: The analog modulator samples the input at 2.8224MHz for fs=44.1kHz. There is no rejection of input signals at those band width which are multiples of the sampling frequency(n x 2.8224MHz ±20.21kHz; n=0,1,2,3...).

## DAC unit :

(Ta=25°C; VA, VD, VB=5.0V±5%; fs=44.1kHz;)

|                    | Parameter            | Symbol | min  | typ   | max   | Units |

|--------------------|----------------------|--------|------|-------|-------|-------|

| Digital filter     |                      |        |      |       |       |       |

| Passband           | (-0.2 dB) (note 1)   | PB     | 0    |       | 20.0  | kHz   |

|                    | (-6.0 dB)            |        | -    | 22.05 | -     | kHz   |

| Stopband           | (note 1)             | SB     | 24.3 |       |       | kHz   |

| Passband ripple    | e                    | PR     |      |       | ±0.05 | dB    |

| Stopband atten     | uation               | SA     | 41   |       |       | dB    |

| Group delay        | (Ts = 1/fs) (note 2) | GD     | -    | 14.7  | -     | Ts    |

| Digital filter + a | nalog filter         |        |      |       |       |       |

| Amplitude chara    | acteristics          |        |      | .0.5  |       | ٩D    |

|                    | 0~20kHz              |        | -    | ±0.5  | -     | dB    |

note 1: The frequencies of passband/stopband are proportional to the sampling frequency (fs); PB=0.4535fs(@-0.2dB), SB=0.546fs(@-41dB).

2: The calculating delay time is occurred by digital filtering. This is the time from the setting 20-bit data on input register to the output of analog signal. (at fs=44.1kHz)

## **DC Characteristics**

## (AVDD=DVDD; AVD, DVB=5.0V±5%; Ta=25°C)

| Paramete                 |          | Symbol | min     | typ | max    | Units |

|--------------------------|----------|--------|---------|-----|--------|-------|

| High level input voltage |          | VIH    | 70%VDD  | -   | -      | V     |

| Low level input voltage  |          | VIL    | -       | -   | 30%VDD | V     |

|                          |          |        |         |     |        |       |

| High level input voltage |          | VOH    | VDD-0.1 | -   | -      | V     |

| lout=-                   | 20uA     |        |         |     |        |       |

| Low level input voltage  |          | VOL    | -       | -   | 0.1    | V     |

| lout=                    | 20uA     |        |         |     |        |       |

|                          |          |        |         |     |        |       |

| Input leak current       | (note 1) | lin    | -       | -   | ±10    | uA    |

| Input leak current       | (note 2) | lid    | -       | 100 | -      | uA    |

| (pull-down pin)          |          |        |         |     |        |       |

note 1: except pull-up/pull-down pin

2: Pull-down pin(Typ 50kΩ) is as follows; PDAD, PDDA,SDIN2,SDDA,SDDA2,TSTI1,TSTI2, TSTO1,TSTO2,TSTO3,OPCL pin.

(Ta=25°C; AVDD,DVDD,AVB,DVB=5.0V; Master clock = 18.432MHz, XTI=384fs [fs=48kHz]; Input 1kHz full scale sine wave input from 2ch analog input pin of ADC and output to 4ch DAC.)

| Power supply                    |     |     |      |       |

|---------------------------------|-----|-----|------|-------|

| Parameter                       | min | typ | max  | Units |

| Power supply current            |     |     |      |       |

| Normal operation (RST=PD="H")   |     |     |      |       |

| AVDD + AVB + DVB                |     | 47  | 70   | mA    |

| DVDD                            |     | 51  | 80   | mA    |

| Power-down mode (RST=PD="L")    |     |     |      |       |

| AVDD + AVB + DVB+ DVDD (note 3) |     | 20  | 250  | uA    |

|                                 |     |     |      |       |

|                                 |     |     |      |       |

| Power dissipation               |     |     |      |       |

| Normal operation                |     | 490 | 750  | mW    |

| Power-down mode                 |     | 0.1 | 1.25 | mW    |

note 3: This is the value in the conditions that external clock(XTI,BCLK,LRCK) is "L", SCLK is "H".

## Switching Characteristics

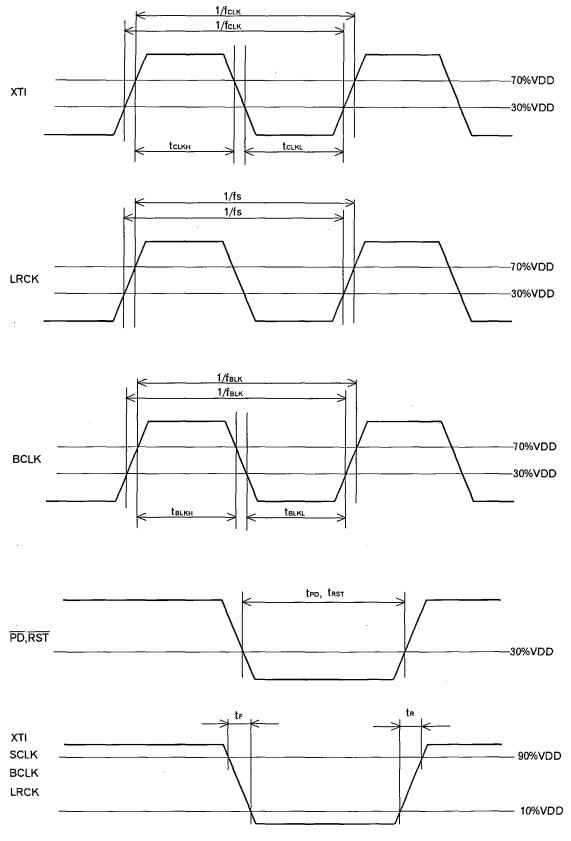

## •Clock

(Ta=25°C; VA, VD, VB=5.0V $\pm$ 5%; CL=20pF)

| Parameter                       |            | Symbol                  | min    | typ     | max    | Units |

|---------------------------------|------------|-------------------------|--------|---------|--------|-------|

| Control clock frequency         |            |                         |        |         |        |       |

| Master clock                    |            |                         |        |         |        |       |

| Quartz oscillator mode          |            |                         |        |         |        |       |

| 256fs:                          |            | fclk                    | 8.192  | 11.2896 | 12.288 | MHz   |

| 384fs:                          |            | <b>f</b> <sub>CLK</sub> | 12.288 | 16.9344 | 18.432 | MHz   |

| 512fs:                          |            | <b>f</b> clk            | 12.288 | 16.384  | 18.432 | MHz   |

| External clock mode             |            |                         |        |         |        |       |

| Duty cycle                      |            |                         | 40     | 50      | 60     | %     |

| 256fs:                          |            | <b>f</b> clk            | 8.192  | 11.2986 | 12.288 | MHz   |

| Pulse                           | width Low  | <b>t</b> clkl           | 30     |         |        | ns    |

| Pulse                           | width High | <b>t</b> clkh           | 30     |         |        | ns    |

| 384fs:                          |            | fclk                    | 12.288 | 16.9344 | 18.432 | MHz   |

| Pulse                           | width Low  | <b>t</b> clkl           | 20     |         |        | ns    |

| Pulse                           | width High | t <sub>clkh</sub>       | 20     |         |        | ns    |

| 512fs:                          |            | fclk                    | 12.288 | 16.384  | 18.432 | MHz   |

| Pulse                           | width Low  | t <sub>clkl</sub>       | 20     |         |        | ns    |

| Pulse                           | width High | t <sub>clkh</sub>       | 20     |         |        | ns    |

| Audio serial data clock (BCLK)  |            | <b>f</b> BLK            | 1.024  | 2.8224  | 3.072  | MHz   |

| Channel select clock (LRCK)     |            | fs                      | 32     | 44.1    | 48     | kHz   |

| Duty cycle                      |            |                         | 49     | 50      | 51     | %     |

| Microcomputer serial data clock | (SCLK      | <b>f</b> <sub>SLK</sub> |        |         | 12.288 | MHz   |

| Pulse                           | width Low  | tslkl                   | 30     |         |        | ns    |

| Pulse                           | width High | <b>t</b> slkh           | 30     |         |        | ns    |

| Reset timing                    |            |                         |        |         |        |       |

| PD pu                           | lse width  | t <sub>PD</sub>         |        | 100     |        | ns    |

| RST p                           | ulse width | t <sub>RST</sub>        |        | 100     |        | ns    |

| Clock falling time              |            |                         |        |         |        |       |

| [XTI, BICK, LRCK, SCLK]         | (note)     | tr                      |        |         |        |       |

| Clock rising time               |            |                         |        |         | 10     | ns    |

| [XTI, BICK, LRCK, SCLK]         | (note)     | tr                      |        |         | 10     | ns    |

note : At input of external CMOS clock for XTI.

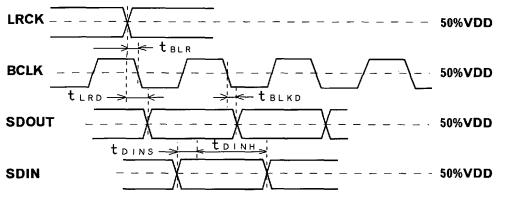

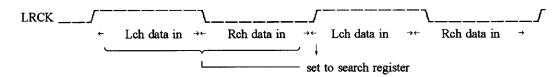

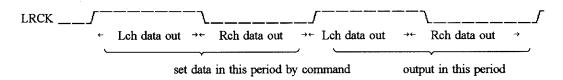

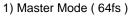

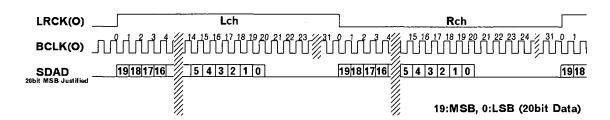

## 1) Audio Interface Timing

(AVDD=DVDD,AVB,DVB=5.0V±5%,Ta=25°C;

Master clock 16.9344MHz,XTI=384fs[fs=44.1kHz]; CL=20pF)

| Parameter                                       | Symbol                  | min                  | typ  | max                  | Units |

|-------------------------------------------------|-------------------------|----------------------|------|----------------------|-------|

| Slave mode                                      |                         |                      |      |                      |       |

| BCLK cycle                                      | t <sub>BLK</sub>        | 312.5                |      |                      | ns    |

| BCLK pulse width Low                            | <b>t</b> BLKL           | 100.0                |      |                      | ns    |

| pulse width High                                | <b>t</b> BLKH           | 100.0                |      |                      | ns    |

| Time from BCLK" $\downarrow$ " to LRCK (note 1) | t <sub>BLR</sub>        | 30-t <sub>BLKH</sub> |      | 30+t <sub>BLKL</sub> | ns    |

| Delay time from LRCK to DOUT(MSB)               | t <sub>LRD</sub>        |                      |      | 70                   | ns    |

| Delay time from BCLK" $\downarrow$ " to DOUT    | <b>t</b> BLKD           |                      |      | 70                   | ns    |

| Latch hold time of SDIN                         | t <sub>DINH</sub>       | 40                   |      |                      | ns    |

| Latch setup time of SDIN                        | t <sub>DINS</sub>       | 40                   |      |                      | ns    |

| Master mode                                     |                         |                      |      |                      |       |

| BCLK cycle                                      | <b>t</b> BLK            |                      | 64fs |                      | ns    |

| Duty cycle                                      |                         |                      | 50   |                      | ns    |

| BCLK pulse width Low                            | t <sub>BLKL</sub>       | 100.0                |      |                      | ns    |

| pulse width High                                | <b>t</b> BLKH           | 100.0                |      |                      | ns    |

| Time from BCLK" $\downarrow$ " to LRCK          | <b>t</b> <sub>BLR</sub> | -20                  |      | 20                   | ns    |

| Delay time from LRCK to DOUT(MSB)               | $\mathbf{t}_{LRD}$      |                      |      | 70                   | ns    |

| Delay time from BCLK" $\downarrow$ " to DOUT    | <b>t</b> BLKD           |                      |      | 70                   | ns    |

| Latch hold time of SDIN                         | t <sub>DINH</sub>       | 40                   |      |                      | ns    |

| Latch set Up time of SDIN                       | toins                   | 40                   |      |                      | ns    |

note 1 : This standard value is provided for not to be overlapped the edge of LRCK and BCLK"<sup>↑</sup>" each other.

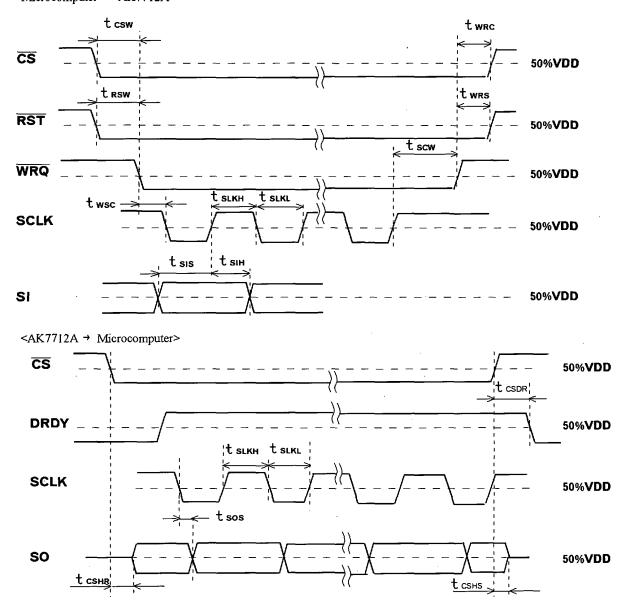

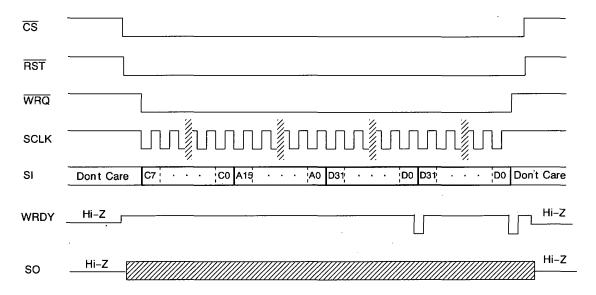

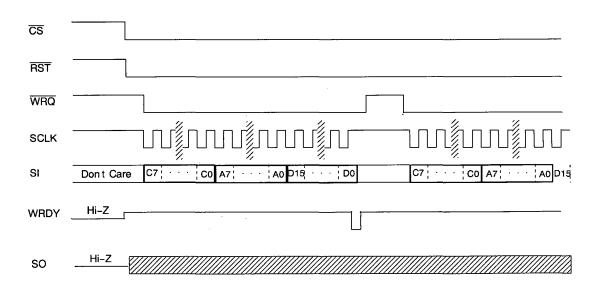

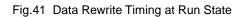

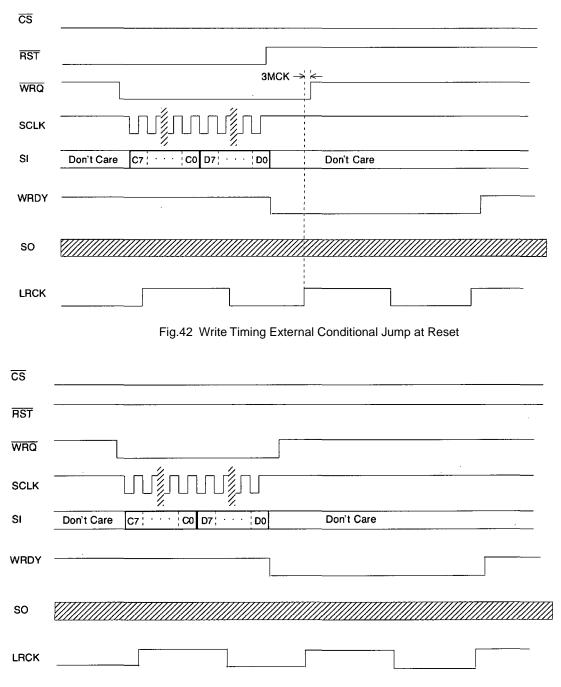

## 2) Microcomputer Interface Timing

$(\textsf{AVDD=DVDD}, \textsf{AVB}, \textsf{DVB=5.0V} \pm 5\%, \textsf{Ta=25^{\circ}C};$

master clock 16.9344MHz,XTI=384fs[fs=44.1kHz];CL=20pF)

| Parameter                                                              | Symbol                   | min        | typ | max | Units |

|------------------------------------------------------------------------|--------------------------|------------|-----|-----|-------|

| From $\overline{CS}"\downarrow"$ to $\overline{WRQ}"\downarrow"$       | t <sub>csw</sub>         | 100        |     |     | ns    |

| From $\overline{RST}$ to $\overline{WRQ}$ " $\downarrow$ "             | t <sub>RSW</sub>         | 100        |     |     | ns    |

| From $\overline{WRQ}$ " $\uparrow$ " to $\overline{CS}$ " $\uparrow$ " | twrc                     | 100        |     |     | ns    |

| From WRQ"↑" to RST"↑"                                                  | t <sub>wrs</sub>         | 100        |     |     | ns    |

| From $\overline{WRQ}$ " $\downarrow$ " to SCLK" $\downarrow$ "         | twsc                     | 100        |     |     | ns    |

| From Last SCLK" <sup>↑</sup> " to WRQ" <sup>↑</sup> "                  | tscw                     | 166(note1) |     |     | ns    |

| SCLK cycle                                                             | <b>t</b> <sub>SLK</sub>  | 200        |     |     | ns    |

| SCLK pulse width Low                                                   | <b>t</b> slkl            | 80         |     |     | ns    |

| pulse width High                                                       | <b>t</b> slkh            | 80         |     |     | ns    |

| SI latch hold time                                                     | t <sub>siH</sub>         | 50         |     |     | ns    |

| SI latch set Up time                                                   | tsis                     | 50         |     |     | ns    |

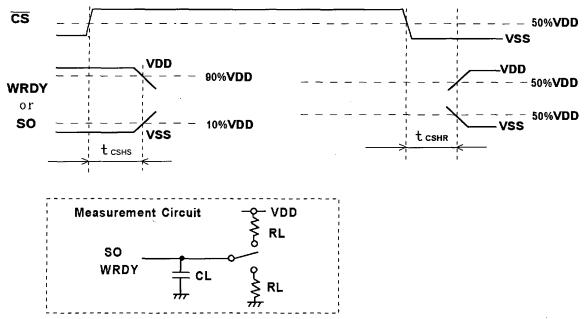

| From $\overline{CS}" \downarrow"$ to                                   | <b>t</b> <sub>CSHR</sub> |            |     | 100 | ns    |

| cancellation of SO,WRDY "Hi-z" (note2)                                 |                          |            |     |     |       |

| From CS"↑" to SO,WRDY"Hi-z" (note2)                                    | t <sub>CSHS</sub>        |            |     | 800 | ns    |

| From CS"↑" to DRDY"↓"                                                  | tcsdr                    |            |     | 100 | ns    |

| From SCLK" $\downarrow$ " to SO setup time (note2)                     | tsos                     |            |     | 40  | ns    |

note 1 : Master clock cycle  $\times$  3

note 2 : See timing chart.

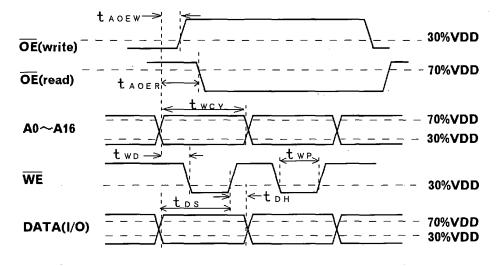

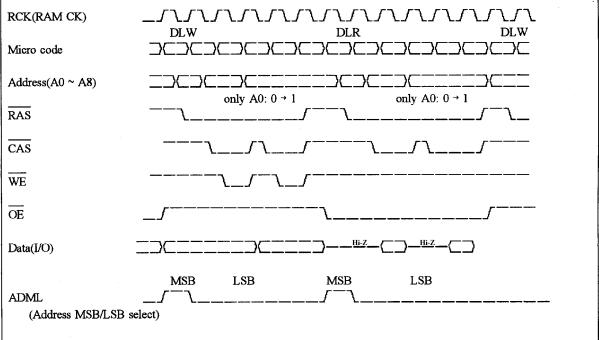

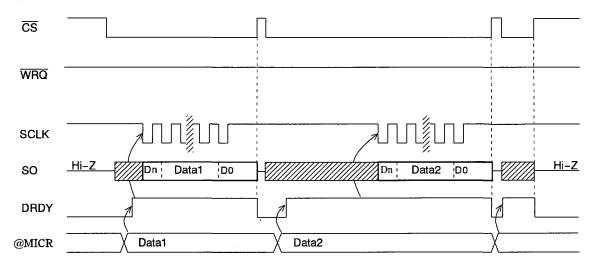

## 3)Read/Write Interface Timing of External RAM (AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

|                                                                  |                   | XTI(MHz) |     |        |     |        |     |       |

|------------------------------------------------------------------|-------------------|----------|-----|--------|-----|--------|-----|-------|

| Parameter                                                        | Symbol            | 18.432   |     | 16.934 |     | 12.288 |     | Units |

|                                                                  |                   | min      | max | min    | max | min    | max |       |

| Address delay time from $\overline{OE}$ " $\uparrow$ " (writing) | t <sub>AOEW</sub> | -15      | 15  | -18    | 18  | -20    | 20  | ns    |

| Address delay time from $\overline{OE} \ "\downarrow"$ (reading) | tAOER             |          | 70  |        | 80  |        | 110 | ns    |

| Access time                                                      | twcy              | 105      |     | 115    |     | 170    |     | ns    |

| Address set-up time                                              | t <sub>wD</sub>   | 10       |     | 12     |     | 15     |     | ns    |

| Data set time                                                    | t <sub>DS</sub>   | 80       |     | 90     |     | 135    |     | ns    |

| Data hold time                                                   | t <sub>DH</sub>   | 10       |     | 12     |     | 15     |     | ns    |

| Pulse width to write                                             | t <sub>WP</sub>   | 60       |     | 70     |     | 90     |     | ns    |

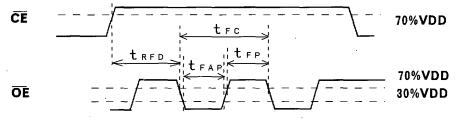

## 4) Refresh Interface Timing of Pseudo SRAM(External RAM)

(AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

|                                |                         | XTI(MHz) |     |        |     |        |     |       |

|--------------------------------|-------------------------|----------|-----|--------|-----|--------|-----|-------|

| Parameter                      | Symbol                  | 18.432   |     | 16.934 |     | 12.288 |     | Units |

|                                |                         | min      | max | min    | max | min    | max |       |

| Auto refresh cycle             | t <sub>FC</sub>         | 145      |     | 162    |     | 210    |     | ns    |

| Pulse width of refresh command | tFAP                    | 80       |     | 90     |     | 135    |     | ns    |

| Delay time of refresh command  | <b>t</b> <sub>RFD</sub> | 100      |     | 110    |     | 160    |     | ns    |

| Pre-charge time of refresh     | t <sub>FP</sub>         | 35       |     | 40     |     | 60     |     | ns    |

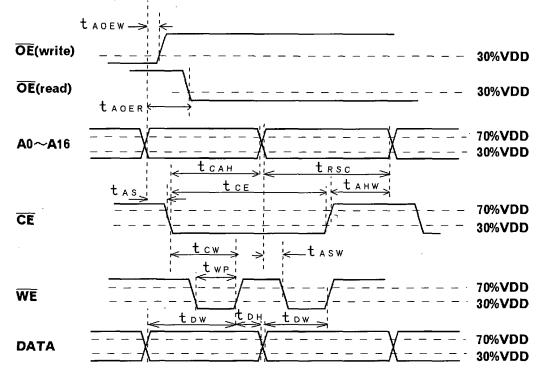

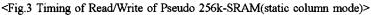

## 5) Read/Write Interface Timing of Pseudo SRAM(External RAM) (Static Column Mode) (AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

|                                                                  |                         |     |     | XTI(I | MHz) |     |     |       |

|------------------------------------------------------------------|-------------------------|-----|-----|-------|------|-----|-----|-------|

| Parameter                                                        | Symbol                  | 18. | 432 | 16.   | 934  | 12. | 288 | Units |

|                                                                  |                         | min | max | min   | max  | min | max |       |

| Address delay time from OE "1" (writing)                         | taoew                   | -15 | 15  | -18   | 18   | -20 | 20  | ns    |

| Address delay time from $\overline{OE}$ " $\uparrow$ " (reading) | <b>t</b> AOER           |     | 70  |       | 80   |     | 110 | ns    |

| Column address hold time                                         | <b>t</b> <sub>CAH</sub> | 110 |     | 120   |      | 170 |     | ns    |

| SC mode read/write cycle                                         | t <sub>RSC</sub>        | 80  |     | 90    |      | 135 |     | ns    |

| Address setup time                                               | tas                     | 10  |     | 12    |      | 15  |     | ns    |

| Pulse width of chip enable                                       | t <sub>CE</sub>         | 180 |     | 200   |      | 280 |     | ns    |

| Column address hold time (after write)                           | tahw                    | 10  |     | 12    |      | 15  |     | ns    |

| Chip enable time                                                 | tcw                     | 95  |     | 105   |      | 140 |     | ns    |

| Column address setup time                                        | tasw                    | 10  |     | 12    |      | 15  |     | ns    |

| Pulse width of write command                                     | twp                     | 35  |     | 40    |      | 60  |     | ns    |

| Data set time                                                    | t <sub>DW</sub>         | 50  |     | 60    |      | 90  |     | ns    |

| Data hold time                                                   | t <sub>DH</sub>         | 10  |     | 12    |      | 15  |     | ns    |

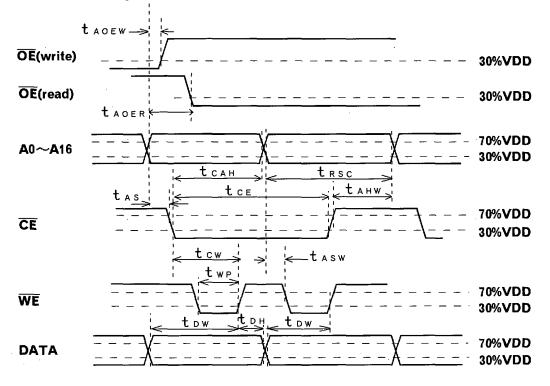

## 6) Read/write Interface Timing of Pseudo SRAM(External RAM) (normal mode) (AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

| Parameter                                                        | Symbol            | 18. | 432 | 16. | 934 | 12.2 | 288 | Units |

|------------------------------------------------------------------|-------------------|-----|-----|-----|-----|------|-----|-------|

|                                                                  |                   | min | max | min | max | min  | max |       |

| Address delay time from $\overline{OE}$ " $\uparrow$ " (writing) | t <sub>AOEW</sub> | -15 | 15  | -18 | 18  | -20  | 20  | ns    |

| Address delay time from $\overline{OE}$ " $\uparrow$ " (reading) | <b>t</b> AOER     |     | 70  |     | 80  |      | 110 | ns    |

| Hold time of column address                                      | tсан              | 110 |     | 120 |     | 170  |     | ns    |

| Address setup time                                               | t <sub>AS</sub>   | 10  |     | 12  |     | 15   |     | ns    |

| Pulse width of chip enable                                       | t <sub>CE</sub>   | 90  |     | 100 |     | 135  |     | ns    |

| Pre-charge time of chip enable                                   | t₽                | 40  |     | 50  |     | 60   |     | ns    |

| Chip enable time                                                 | t <sub>cw</sub>   | 90  |     | 100 |     | 135  |     | ns    |

| Pulse width of write command                                     | twp               | 35  |     | 40  |     | 60   |     | ns    |

| Data set time                                                    | t <sub>DW</sub>   | 100 |     | 110 |     | 160  |     | ns    |

| Data hold time                                                   | t <sub>DH</sub>   | 10  |     | 12  |     | 15   |     | ns    |

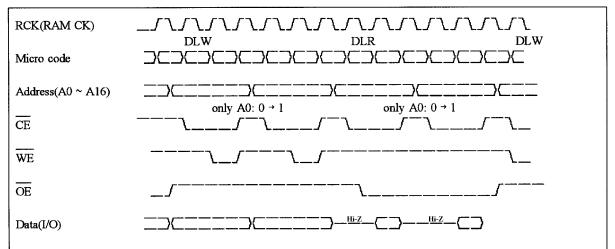

# 7) Refresh Interface Timing of DRAM(External RAM) (CAS before RAS Refresh) (AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

|                                    |                         | XTI(MHz) |     |        |     |        |     |       |

|------------------------------------|-------------------------|----------|-----|--------|-----|--------|-----|-------|

| Parameter                          | Symbol                  | 18.432   |     | 16.934 |     | 12.288 |     | Units |

|                                    |                         | min      | max | min    | max | min    | max |       |

| Read cycle                         | <b>t</b> CRD            | 240      |     | 260    |     | 360    |     | ns    |

| Pulse width of RASCE"H"            | twrn                    | 105      |     | 120    |     | 170    |     | ns    |

| Pulse width of RASCE"L"            | twrl                    | 105      |     | 120    |     | 170    |     | ns    |

| RASCE Pre-charge • CASRF hold time | <b>t</b> <sub>RPC</sub> | 80       |     | 90     |     | 130    |     | ns    |

| CASRF setup time at auto refresh   | tsur                    | 10       |     | 12     |     | 15     |     | ns    |

| CASRF hold time at auto refresh    | tHRRC                   | 200      |     | 220    |     | 320    |     | ns    |

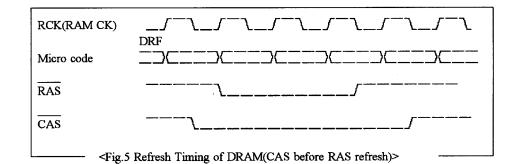

8) Read/Write Interface Timing of DRAM(External RAM) (Page Mode) (AVDD,DVDD,AVB,DVB=5.0V±5%, Ta=25°C, CL=20pF)

| Parameter                                                       | Symbol                   | 18.4 | 432 | 16. | 934 | 12. | 288 | Units |

|-----------------------------------------------------------------|--------------------------|------|-----|-----|-----|-----|-----|-------|

|                                                                 |                          | min  | max | min | max | min | max |       |

| Address delay time fromOE "↑" (write)                           | t <sub>AOEW</sub>        | -15  | 15  | -18 | 18  | -20 | 20  | ns    |

| Address delay time from $\overline{OE}$ " $\downarrow$ " (read) | t <sub>AOER</sub>        |      | 70  |     | 80  |     | 110 | ns    |

| RASCE preceded address setup time                               | tsura                    | 10   |     | 12  |     | 15  |     | ns    |

| RASCE followed address hold time                                | t <sub>HRA</sub>         | 12   |     | 14  |     | 18  |     | ns    |

| CASRF preceded address setup time                               | <b>t</b> <sub>SUCA</sub> | 10   |     | 12  |     | 15  |     | ns    |

| CASRF followed address hold time                                | <b>t</b> HCLCA           | 45   |     | 45  |     | 60  |     | ns    |

| CASRF hold time after write                                     | t <sub>HWCH</sub>        | 40   |     | 43  |     | 60  |     | ns    |

| Write hold time after CASRF                                     | tHCLW                    | 55   |     | 65  |     | 90  |     | ns    |

| Write pulse width                                               | tw                       | 40   |     | 43  |     | 60  |     | ns    |

| Data setup time                                                 | t <sub>sud</sub>         | 0    |     | 0   |     | 0   |     | ns    |

| Data hold time after write                                      | t <sub>HWLD</sub>        | 60   |     | 70  |     | 100 |     | ns    |

| Pulse width of CASRF"H"                                         | t <sub>wcн</sub>         | 22   |     | 24  |     | 32  |     | ns    |

| Pulse width of CASRF"L"                                         | twcL                     | 54   |     | 62  |     | 90  |     | ns    |

## Timing Waveform

Audio Interface Timing

Microcomputer Interface Timing <Microcomputer → AK7712A>

Microcomputer Interface Timing (Supplement)

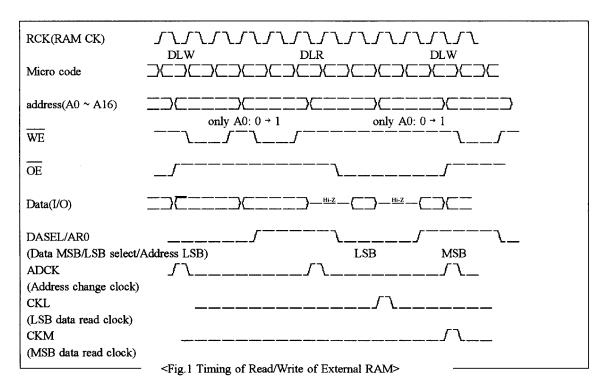

Read/Write Interface Timing of External SRAM

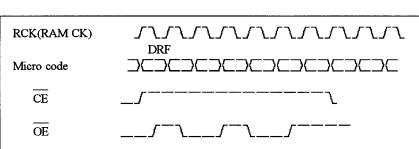

Refresh Interface Timing of Pseudo SRAM

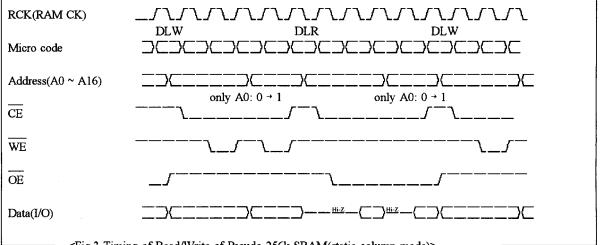

Read/Write Interface Timing of Pseudo SRAM (Static Column Mode)

Read/Write Interface Timing of Pseudo SRAM (Normal Mode)

Refresh Interface Timing of DRAM (CAS before RAS Refresh)

RASCE

$$t_{CRD}$$

$t_{CRD}$

$70\%VDD$

$t_{WRH}$

$t_{WRL}$

$t_{RPC}$

$t_{SUR}$

$t_{RRC}$

$t_{RRC}$

$t_{RPC}$

$t_{SUR}$

$t_{RRC}$

$t_{RRC}$

Read/Write Interface Timing of DRAM (Page Mode)

|           | t adew->' (<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| OE(write) | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30%VDD           |

| OE(read)  | t AOER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70%VDD           |

| A0~A8     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70%VDD<br>30%VDD |

| RASCE     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70%VDD<br>30%VDD |

| CASRF     | $\frac{t_{suca}}{v_{c}} \stackrel{t_{c}}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}}{\overset{c}{\overset{c}{\overset{c}{\overset{c}{\overset{c}}{\overset{c}{\overset{c}}}}}}}}}$ | 70%VDD<br>30%VDD |

|           | ¦t н с¦∟ w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

| WE        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70%VDD<br>30%VDD |

| DATA      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70%VDD<br>30%VDD |

#### **Function Manual**

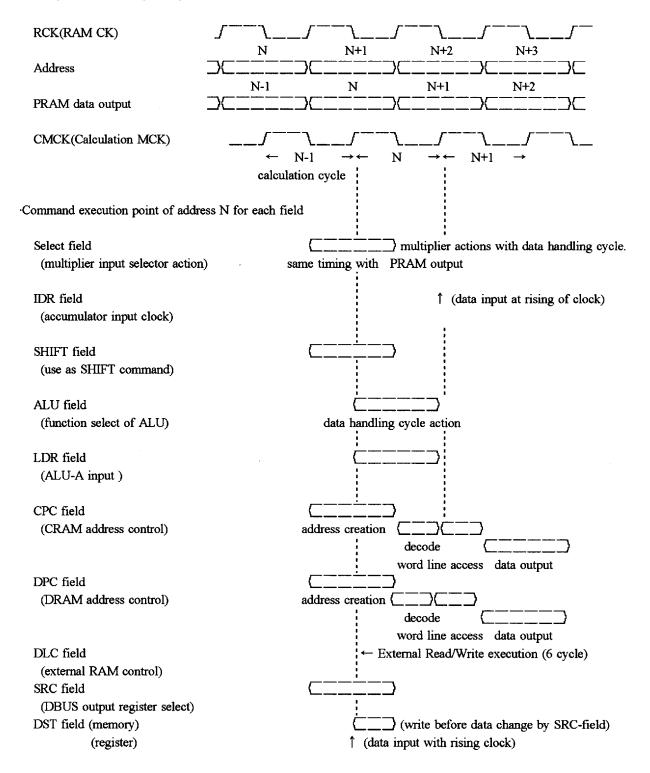

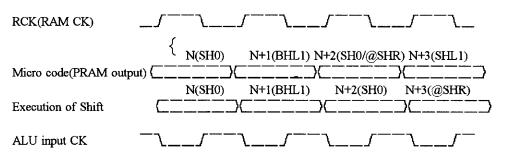

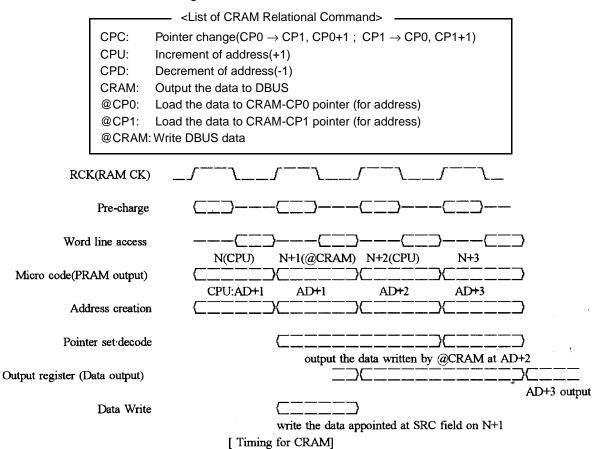

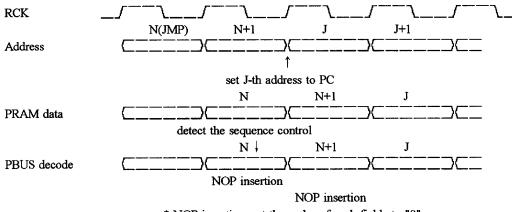

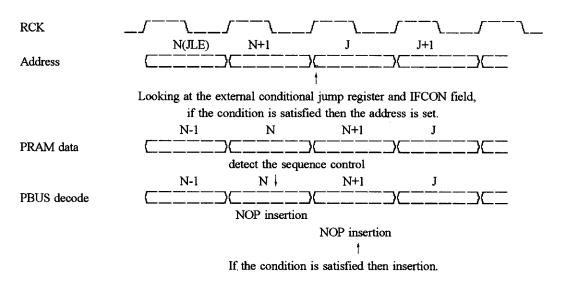

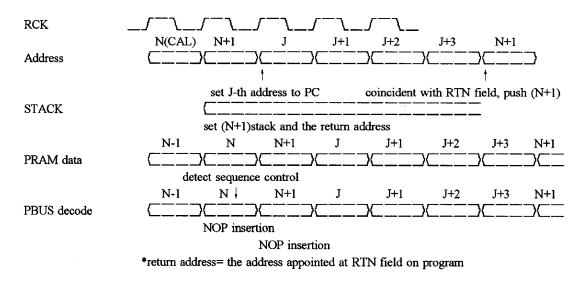

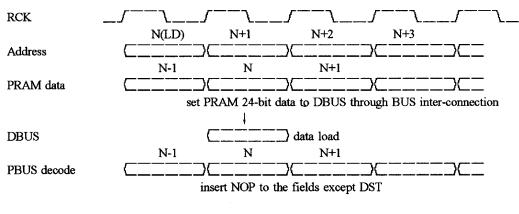

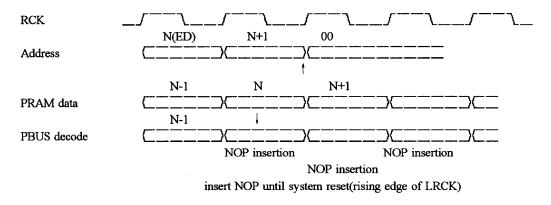

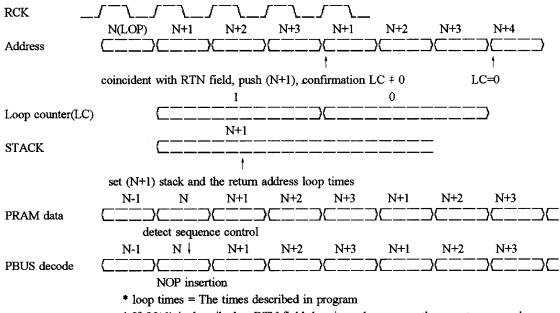

#### ■ DSP unit : Execution Timing of Each Command

Each Blocks(PRAM,DRAM,CRAM,Calculation unit,etc.) actions on pipeline. On controlling of this pipeline, each stages(command fetch, command decode and execution) are handled in parallel. The operations for each block is executed by 32-bit holizontal code. Therefore each operations are executed equivalently in one machine cycle. The following is the executing timing of each command.

## Calculation Function

## 1) Arithmetic System

| 1                                                                                                                                         | (S) shows the sign bit of data)                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| multiplier input regis<br>(16-bit)                                                                                                        | 0 -15<br>S15<br>S23                                                                     |

| multiplier input regis<br>(24-bit)                                                                                                        |                                                                                         |

| multiplier output                                                                                                                         | 0 -29 -38<br>[\$][\$][\$][\$][]][][][][][]][][][]][][]]                                 |

|                                                                                                                                           | (It's extended 1 bit not to overflow at the case of $-1 \times -1$ .)                   |

| ALU-B input<br>shift output (34-bit)                                                                                                      | 0 -29<br>SISISISIS                                                                      |

| <the above="" i<="" is="" td=""><td>in the case that the data is not shifted. Detail is mentioned in the section of shift.&gt;</td></the> | in the case that the data is not shifted. Detail is mentioned in the section of shift.> |

| ALU-A input (34-bit)                                                                                                                      | 0 -29<br>SICICICICICICICICICICICICICICICICICICIC                                        |

|                                                                                                                                           |                                                                                         |

| DR0 ~ 3<br>(34-bit)                                                                                                                       | 0<br>300000000000000000000000000000000000                                               |

| DR0 ~ 3 → DBUS                                                                                                                            | 0<br>Socooooooooooooooooooooooooooooooooooo                                             |

It's possible to handle a real number of 2's complement. The following is typical processing of data.

| << DBUS $\rightarrow$ register,etc. >> Except for @IORL, take data from MSB. |                                                            |  |  |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|

| DRAM(24-bit)                                                                 | 0 -23<br>Sinnanananananananananananananananananan          |  |  |  |  |

| I/O register<br>(@IORL)                                                      | -16 -23<br>* * * * * * * * * * * * * * * •                 |  |  |  |  |

| << register,etc. → DBU<br>Except for IORL an                                 | JS >><br>d ODRB, output data from MSB.                     |  |  |  |  |

| DRAM(24-bit)                                                                 | 0 -23<br>Social -23                                        |  |  |  |  |

| I/O register(16-bit)                                                         | 0 -15<br><b>S</b><br>(LSB-8bit="0")                        |  |  |  |  |

| IORL(8-bit)                                                                  | 0 -15 -23<br><u>0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 </u> |  |  |  |  |

| ODRB(21-bit)<br>(MSB                                                         | -23<br>- 3 bits = "0")                                     |  |  |  |  |

## ASAHI KASEI

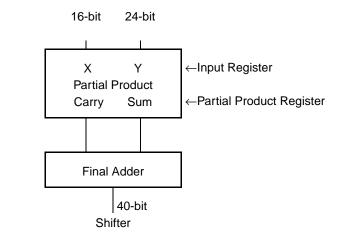

## 2) Multiplier

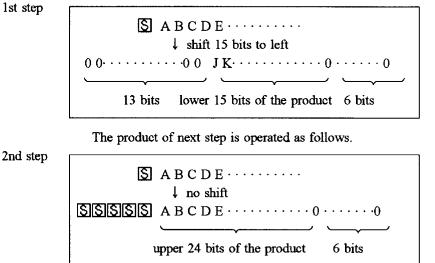

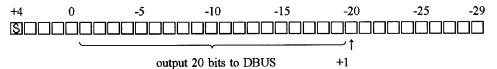

Multiplier outputs the 31-bit data for shift circuit as a result of fixed-point calculation(24-bit(data)  $\times$  16-bit(coefficient) = 40-bit). 4 ways of multiplication can operate for the data as follows. The output data is extended from MSB for reason that the data overflows at -1  $\times$  -1. The following combinations are possible for input.

| ſ |                 |              |                               |

|---|-----------------|--------------|-------------------------------|

|   | 16-bit Input    | 24-bit Input | notes                         |

|   | Coefficient RAM | Data RAM     |                               |

|   | Coefficient RAM | DBUS         |                               |

|   | DBUS            | Data RAM     |                               |

|   | DBUS            | DBUS         | calculation of X <sup>2</sup> |

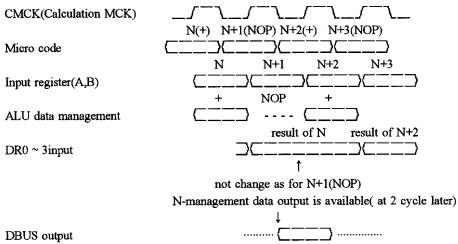

Multiplication actions always synchronous with CMCK, the product is output in 2 cycles.

| CMCK(Calculation MCK)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |